# S9121

## **GS9121**

## 1.0A/2.0A High-Side Power Switch With Flag

## **Product Description**

The GS9121 serial products are high-side power switch with  $80m\Omega$  R<sub>DS(ON)</sub>, available with 1.0A and 2.0A continuous output capability. They are suitable for 3.0V, 3.3V and 5.0V power rail.

GS9121 has enable pin with selectable active high or active low level. It has output discharge feature. It has FLAG pin to indicate the chip status, active low with open drain output once OCP, load short, OTP or OUT-to-IN reverse event is triggered.

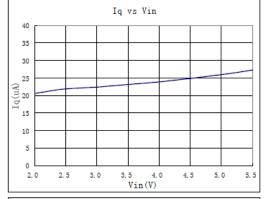

GS9121 has lower quiescent current as 25uA making this device ideal for portable battery-operated equipment. Available Package: SOT-23-5L.

#### **Features**

- Integrated high-side Power MOS: 80m Ω (Typ.)

- Operation Voltage: 2.5V to 5.5V

- Compliant to USB Specifications

- Quiescent Current: 25uA(Typ.)

- Shutdown current: 1.0uA(Max.)

- Enable active level selectable: High/Low

- Output discharge feature

- Continuous current: 1.0A/2.0A

- Open-Drain Fault Flag Output

- Hot Plug-In Application (Soft-Start)

- Current Limiting Protection

- Thermal Shutdown Protection

- Reverse Current Flow Blocking (no body diode)

- RoHS Compliant, 100%Pb & Halogen Free

- Device Meets MSL 3 Requirements

#### **Applications**

- Notebook & Ultrabook

- Tablet, PAD

- USB 2.0/3.0 Port

- LVDS Port, HDMI Port, DP Port

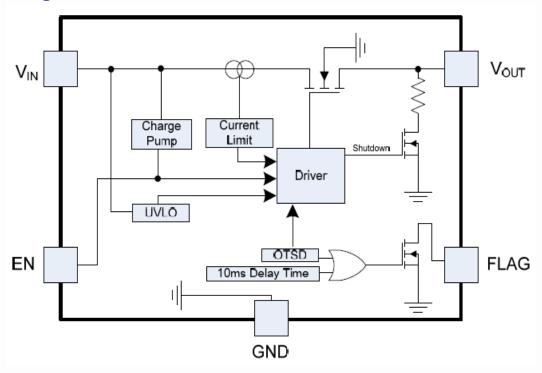

#### **Block Diagram**

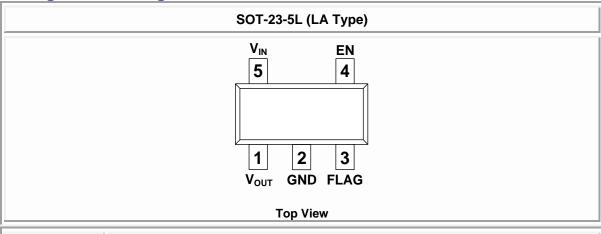

## Packages & Pin Assignments

| Pin Name         | Description                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND              | GND Pin.                                                                                                                                                                         |

| Vin              | Power supply input pin, using 1.0uF bypass capacitor is enough in most applications, if the distance is long in layout, please using 10uF or larger capacitor close to the chip. |

| EN               | Enable pin, active low or high. Must be set high or low, cannot be left floating.                                                                                                |

| V <sub>OUT</sub> | Output pin, using 1.0uF bypass capacitor is enough in most applications, if the distance is long in layout, please using 10uF or larger capacitor close to the chip.             |

| FLAG             | Flag output with open drain, active low. Connect a pull-up resistor (10k) to input.                                                                                              |

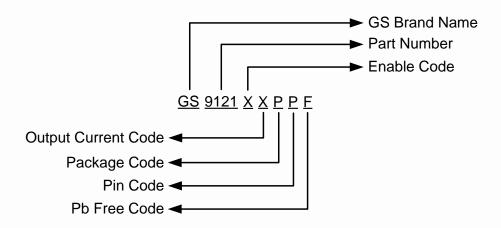

## **Ordering Information**

| Part Number | Output Current | Enable      | Marking ID | Package   |

|-------------|----------------|-------------|------------|-----------|

| GS9121ABLAF | 1.0A           | Active High | PBXWG      | SOT-23-5L |

| GS9121BBLAF | 1.0A           | Active Low  | pBXWG      | SOT-23-5L |

| GS9121ADLAF | 2.0A           | Active High | PEXWG      | SOT-23-5L |

| GS9121BDLAF | 2.0A           | Active Low  | pAXWG      | SOT-23-5L |

<sup>\*</sup>GS9121Ax, Enable pin-active high, XWG=GS code \*GS9121Bx, Enable pin-active low, XWG=GS code

#### **Absolute Maximum Ratings (Note 2)**

| Symbol            | Parameter Parameter                             | Value       | Units |

|-------------------|-------------------------------------------------|-------------|-------|

| V <sub>IN</sub>   | Input Voltage                                   | 6.0         | V     |

| V <sub>EN</sub>   | Input Voltage for Enable                        | -0.3 to 6.0 | V     |

| $V_{FLG}$         | Flag Voltage                                    | 6.0         | V     |

| P <sub>D</sub>    | Power Dissipation@ T <sub>A</sub> =25°C         | 0.4         | W     |

| TJ                | Operating Junction Temperature                  | 125         | °C    |

| T <sub>STG</sub>  | Storage Temperature Range                       | -65 to +150 | °C    |

| T <sub>LEAD</sub> | Lead Temperature(Soldering, 10 sec)             | 260         | °C    |

| $\theta_{JA}$     | Thermal Resistance Junction to Ambient (Note 2) | 250         | °C/W  |

| θјс               | Thermal Resistance Junction to Case (Note 2)    | 100         | °C/W  |

| TA                | Operating Ambient Temperature Range             | -40 to +85  | ∘C    |

| FOD               | Machine Model                                   | 200         | V     |

| ESD               | Human Body Model                                | 4000        | V     |

Note 1: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

Note 2: Using 2oz dual layer (Top, Bottom) FR4 PCB with 4x4mm<sup>2</sup> cooper as thermal PAD.

#### **Electrical Characteristics (Note 3)**

Test Condition:  $C_{IN}=C_{OUT}=1.0$ uF,  $V_{IN}=5.0$ V,  $R_L=10$ Ω,  $C_L=10$ uF unless otherwise specified, all limits are test at  $T_A=25$ °C, and bold type is limited at  $T_A=-40$  to 85°C.

| Symbol               | Parameter                                              |                 | Test Conditions                                                                 | Min  | Тур | Max | Unit |

|----------------------|--------------------------------------------------------|-----------------|---------------------------------------------------------------------------------|------|-----|-----|------|

| Vin                  | Input Voltage Range                                    |                 | -                                                                               | 2.5  | -   | 5.5 |      |

| Vuvlo                | UVLO Threshol                                          | d               | -                                                                               | 1.3  | 1.7 | -   | V    |

| Vuvlohy              | UVLO Hysteres                                          | is              | -                                                                               | -    | 0.1 | -   |      |

| I <sub>SHDN</sub>    | Shutdown Quie                                          | scent Current   | Switch off, Vout=OPEN                                                           | -    | 0.1 | 1.0 | μA   |

| Ιq                   | Quiescent Curre                                        | ent             | Switch on, Vout=OPEN                                                            | -    | 25  | 45  | μA   |

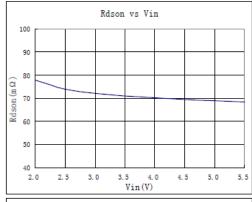

| <b>.</b>             | 0 11 0 0 1                                             |                 | V <sub>IN</sub> =5V, I <sub>OUT</sub> =0.5A                                     | -    | 80  | 100 | mΩ   |

| R <sub>DS(ON)</sub>  | Switch On Resi                                         | stance          | V <sub>IN</sub> =5V, I <sub>OUT</sub> =1.0A                                     | -    | 80  | 100 |      |

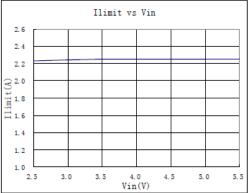

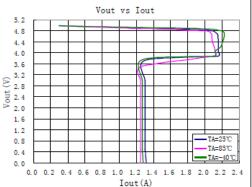

|                      |                                                        | GS9121xB (1.0A) | Current Ramp (<0.1A/ms)                                                         | 1.2  | 1.5 | 1.7 | А    |

| I <sub>LMT</sub>     | Current Limit                                          | GS9121xD (2.0A) |                                                                                 | 2.3  | 2.5 | 2.7 |      |

|                      | Fold-back                                              | GS9121xB (1.0A) | ., .,                                                                           | -    | 0.8 | -   | А    |

| I <sub>SHORT</sub>   | Short Current                                          | GS9121xD (2.0A) | V <sub>OUT</sub> =0V                                                            | - 1  | 1.6 | -   |      |

| I <sub>LEAKAGE</sub> | Leakage Current (V <sub>IN</sub> to V <sub>OUT</sub> ) |                 | Disable EN pin, V <sub>OUT</sub> =0V                                            | - 1  | 0.5 | 10  | μA   |

| I <sub>REVERSE</sub> | Reverse Current (V <sub>OUT</sub> to V <sub>IN</sub> ) |                 | Disable EN pin, V <sub>OUT</sub> >V <sub>IN</sub>                               | - 1  | 0.5 | 10  | μA   |

| $V_{ENH}$            | Enable High Input Threshold                            |                 | -                                                                               | 2.0  | -   | -   | V    |

| V <sub>ENL</sub>     | Enable Low Input Threshold                             |                 | -                                                                               | -    | - 1 | 0.8 | V    |

| I <sub>EN</sub>      | Enable Pin Input Current (Note 4)                      |                 | Force 0V to 5.5V at EN pin                                                      | -1.0 | - 1 | 1.0 | μA   |

| R <sub>PULL</sub>    | Output pull-low resistor                               |                 | with discharge device                                                           | -    | 75  | 150 | Ω    |

| ton                  | Output Rising Time                                     |                 | From EN active to output rising 90%, V <sub>IN</sub> =5.0V, R <sub>L</sub> =10Ω | -    | 0.4 | -   | ms   |

| tFLAG_D              | FLAG response delay time                               |                 | From OCP trigger to FLAG active                                                 | 5    | 10  | 15  | ms   |

#### **Electrical Characteristics (Continue)**

Test Condition:  $C_{IN}=C_{OUT}=1.0 uF$ ,  $V_{IN}=5.0 V$ ,  $R_L=10 \Omega$ ,  $C_L=10 uF$  unless otherwise specified, all limits are test at  $T_A=25 °C$ , and bold type is limited at  $T_A=-40 to 85 °C$ .

| Symbol          | Parameter                    | Test Conditions            | Min | Тур  | Max Unit |

|-----------------|------------------------------|----------------------------|-----|------|----------|

| RFLAG           | FLAG output resistance       | Isink=1mA                  |     | 20   | 400 Ω    |

| IFLAG_L         | FLAG pin leakage             | FLAG disactive, force 5.0V | -   | 0.01 | 1.0 µA   |

| Тотр            | Thermal shutdown temperature | -                          | -   | 130  | - °C     |

| T <sub>HY</sub> | Thermal shutdown hysteresis  | -                          | -   | 20   | - °C     |

Note 3: All devices are 100% production tested at T<sub>A</sub>=+25°C; all specifications over the automotive temperature range is guaranteed by design, not production tested. Parameter is guaranteed by design.

Note 4: No parasitic diode between EN pin and V<sub>IN</sub> pin.

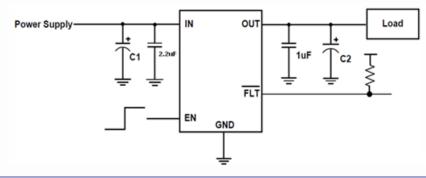

## **Typical Applications**

## **Typical Performance Characteristics**

#### **Application Information**

#### **Input and Output**

IN (input) is the chip power supply connection to the logic circuit and the drain of the power MOSFET. OUT (output) is connected Source of the power MOSFET. In typical application, current flows through the MOSFET channel from IN to OUT.

#### **Thermal Shutdown**

Thermal shutdown is employed to protect the device from damage if the die temperature exceeds approximately 130°C. If enabled, the switch automatically restarts when the die temperature falls 20°C. The output and FLG signal will continue to cycle on and off until the device is disabled or the fault is removed.

#### **Power Dissipation**

The low on-resistance on the N-channel MOSFET allows the small surface-mount packages to pass large currents. It is good design practice to check power dissipation and junction temperature for each application. Begin by determining the  $R_{DS(ON)}$  of the N-channel MOSFET relative to the input voltage and operating temperature. Using the highest operating ambient temperature of interest and  $R_{DS(ON)}$ , the power dissipation per switch can be calculated by:

$P_D = R_{DS(ON)} \times I^2$

Finally, calculate the junction temperature:

$T_J = P_D x R_{\theta JA} + T_A$

Where:

$T_A$  = Ambient temperature

R<sub>0JA</sub> = Thermal resistance

$P_D$  = Total power dissipation

#### **UVLO**

Under-voltage lockout (UVLO) prevents the MOSFET switch from turning on until input voltage exceeds approximately 1.7V. If input voltage drops below approximately 1.6V, UVLO turns off the MOSFET switch, FLG will be asserted accordingly. Under-voltage detection functions only when the switch is enabled.

#### **Current Limiting and Short-Circuit Protection**

The current limit circuitry prevents damage to the MOSFET switch and the hub downstream port but can deliver load current up to the current limit threshold of typically 1A/2.1A through the switch of GS9121xB/xD. When a heavy load or short circuit is applied to an enabled switch, a large transient current may flow until the current limit circuitry responds. Once this current limit threshold is exceeded the device enters constant current mode until the thermal shutdown occurs or the fault is removed.

#### **FLAG Function**

The FLAG is output to indicate over current, load short, over temperature trigger events. It is active low with open-drain output after 10ms(Typ.) deglitch timeout. The output remains asserted until the over-current condition is removed. Over temperature condition is also reported immediately.

#### **Supply Filtering**

In most applications, two 1.0µF bypass capacitors between IN to GND and OUT to GND, close to the chip are strongly recommended to depress supply transients. For long distance layout, larger bypass cap is necessary, like 22µF, 47µF or larger. Without a bypass capacitor, it may cause significant ringing on the input (from supply lead inductance) which could damage the chip during load short. Input transients must not exceed the absolute maximum supply voltage (6.0V) even for a short duration.

#### **Enable Pin**

EN pin must be driven logic high or low for a clearly defined input. Floating this pin may cause unpredictable operation. EN pin should not be allowed to go negative voltage comparison to GND. There is no parasitic ESD Diodes between EN pin and IN pin.

#### **Layout Considerations**

For best performance of the GS9121 series, the following guidelines muse be strictly followed:

- 1. Input and output capacitors should be placed close to the IC and connected to ground plane to reduce noise coupling.

- 2. The GND should be connected to a strong ground plane for heat sink.

- 3. Keep the main current traces as possible as short and wide.

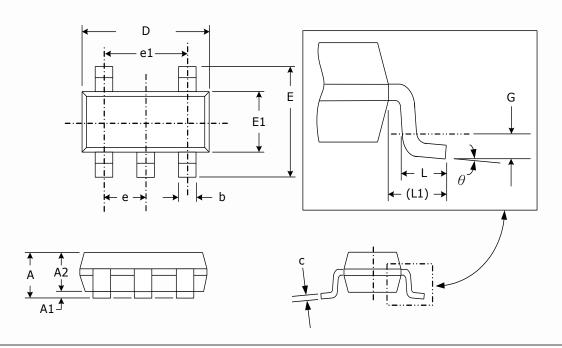

## **Package Dimension**

## **SOT-23-5L**

|         |             | Dimension | ıs     |       |  |

|---------|-------------|-----------|--------|-------|--|

| SYMBOL  | Millimeters |           | Inches |       |  |

| STWIBUL | MIN         | MAX       | MIN    | MAX   |  |

| A       | 0.950       | 1.450     | 0.037  | 0.057 |  |

| A1      | 0.050       | 0.150     | 0.002  | 0.006 |  |

| A2      | 0.900       | 1.300     | 0.035  | 0.051 |  |

| b       | 0.300       | 0.500     | 0.012  | 0.020 |  |

| С       | 0.080       | 0.200     | 0.003  | 0.008 |  |

| D       | 2.800       | 3.000     | 0.110  | 0.118 |  |

| E       | 2.600       | 3.000     | 0.102  | 0.118 |  |

| E1      | 1.500       | 1.700     | 0.059  | 0.067 |  |

| е       | 0.950       | (TYP)     | 0.037  | (TYP) |  |

| e1      | 1.900       | (TYP)     | 0.075  | (TYP) |  |

| L       | 0.350       | 0.550     | 0.014  | 0.022 |  |

| L1      | 0.600       | (TYP)     | 0.024  | (TYP) |  |

| G       | 0.250       | (TYP)     | 0.010  | (TYP) |  |

| θ       | 0°          | 8°        | 0°     | 8°    |  |

## **NOTICE**

Information furnished is believed to be accurate and reliable. However Globaltech Semiconductor assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties, which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Globaltech Semiconductor. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information without express written approval of Globaltech Semiconductor.

## **CONTACT US**

| GS Headquarter |                                                                                      |  |

|----------------|--------------------------------------------------------------------------------------|--|

| \              | 4F.,No.43-1,Lane11,Sec.6,Minquan E.Rd Neihu District Taipei City 114, Taiwan (R.O.C) |  |

| Co             | 886-2-2657-9980                                                                      |  |

| Q:::•\         | 886-2-2657-3630                                                                      |  |

| <u> </u>       | sales_twn@gs-power.com                                                               |  |

|     | RD Division                          |  |  |

|-----|--------------------------------------|--|--|

| \\\ | 824 Bolton Drive Milpitas. CA. 95035 |  |  |

| E   | 1-408-457-0587                       |  |  |